In high-speed digital circuit design, maintaining a balance between Power Integrity (PI) and Signal Integrity (SI) is critical. The design of coupling vias between power and ground planes significantly impacts this balance. This article explores optimization strategies for these coupling vias and their quantitative evaluation methods to achieve optimal electrical performance.

Fundamental Principles of Coupling Vias

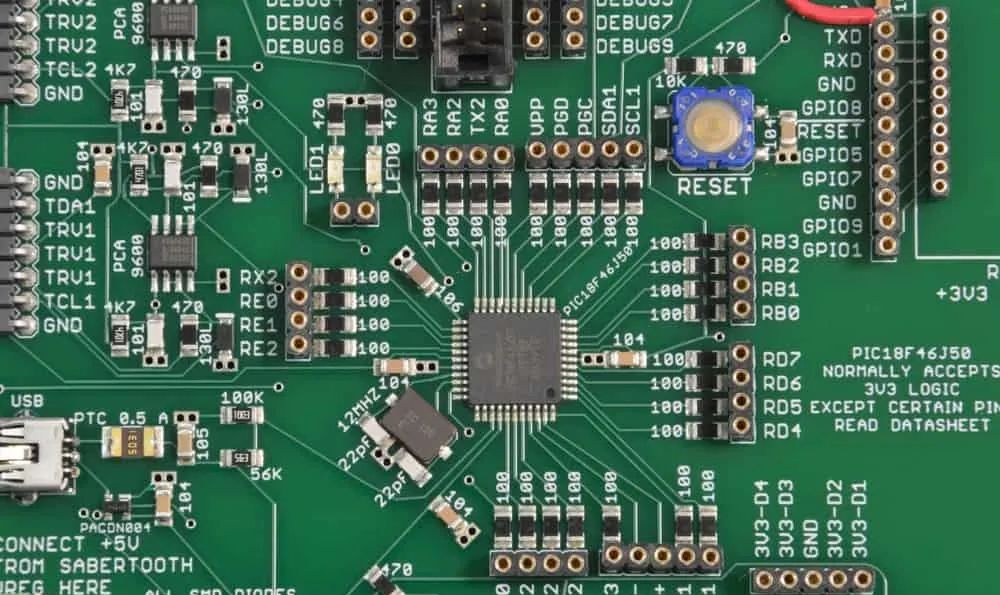

In multilayer PCBs, the power and ground planes are typically interconnected through decoupling capacitors to form a low-impedance path that suppresses power noise. However, conventional via structures introduce parasitic inductance, which increases impedance at high frequencies, reducing the effectiveness of decoupling. Optimized coupling via designs can significantly improve this issue.

In the Power Distribution Network (PDN), the equivalent circuit model of a coupling generally includes series inductance (Ls) and parallel capacitance (Cp). When the operating frequency approaches the self-resonant frequency (SRF) of the via structure, the impedance characteristics undergo significant changes, directly impacting decoupling performance.

Quantitative Evaluation Methods

1. Input Impedance Measurement

Using a Vector Network Analyzer (VNA), the S-parameters of the coupling via structure can be measured to calculate its input impedance frequency response. Key evaluation metrics include:

Z_PDN(f): PDN impedance variation over frequency

Target Impedance: Typically calculated as 1% of the power supply voltage divided by the maximum transient current

Impedance Valley Frequency: Frequency at which impedance is at its lowest

2. Time-Domain Reflectometry (TDR) Analysis

A Time-Domain Reflectometer (TDR) can measure the time-domain characteristics of the coupling via, providing insights into:

Rise Time Impact: How the via affects signal transitions

Reflection Coefficient: Measurement of impedance mismatches

Time Delay: Delay introduced by the via structure

3. Eye Diagram Analysis

Eye diagrams are used to evaluate signal integrity. Critical parameters include:

Eye Height: Indicating noise-induced degradation

Eye Width: Reflecting timing jitter effects

Eye Area: A comprehensive performance indicator

Optimization Strategies for Coupling Vias

1. Geometrical Optimization

Via Array Configuration: Using multiple small vias instead of a single large via to reduce parasitic inductance

Buried/Blind Vias: Minimizing interlayer interference

Optimized Via Pitch: Determining optimal spacing based on skin effect calculations

Pad and Solder Mask Design: Adjusting dimensions to optimize signal transitions

2. Decoupling Network Optimization

Distributed Decoupling: Proper capacitor placement significantly influences PDN impedance in high-frequency PCBs

Capacitor Value Gradient: Using a range of capacitance values from nF to μF to improve broadband decoupling

X2Y Capacitors: Reducing Equivalent Series Inductance (ESL) for improved high-frequency performance

3. Power Plane Design Optimization

Split Plane Management: Preventing disruptions in return current paths

Grid Ground Implementation: Creating a uniform decoupling path in specific applications

Embedded Capacitance Planes: Reducing layer spacing to increase plane capacitance

Quantitative Trade-off Analysis Between Decoupling and Signal Integrity

In practical designs, decoupling effectiveness often conflicts with signal integrity. Quantitative evaluation methods include:

Composite Index Formula:

SI_PI_Balance=α×Z_PDN(f)+β×Jitter+γ×EMI

where α, β, γ are weight coefficients based on application requirements

Monte Carlo Simulation: Evaluating design robustness by considering manufacturing tolerances

Performance-Cost Ratio (PCR):

PCR = System Performance Improvement/Manufacturing Cost Increase

Optimizing power and ground plane coupling vias is an essential aspect of high-speed PCB design. Designers can achieve optimal system performance by quantitatively assessing the trade-off between decoupling efficiency and signal integrity. Engineers should choose the appropriate via structures and evaluation methods based on specific application requirements to ensure the reliability and performance of electronic systems.

For practical applications, combining electromagnetic field simulations with circuit simulations is recommended to predict via performance, with real-world measurements used to validate design effectiveness.